Intel recently unveiled its newest 10nm atom architecture during the Linley Fall Processor Conference. This ultra-low-power (ULP) architecture is not comparable to Intel’s venerable Core chip series, but it powered countless ULP devices.

Among these ULP devices are the Internet of Things devices, tablets, and micro-servers. These segments are still Intel’s bastion, given the fact that AMD can’t compete in these areas.

This giant step toward 10nm Tremont architecture starts with focusing on single-sequence performance, while also bringing bigger improvements. These improvements come in the form of L2 cache addition, new instruction support, and heightened security.

A big reveal from today’s Linley Fall Processor Conference—the first details on #Tremont, our next generation low power X86 architecture. Our Tremont Chief Architect calls it “a world-class CPU architecture designed for enhanced processing power in compact, low power packages.”

— Intel (@intel) October 24, 2019

Intel revealed that these efforts ended with a 30% increase in IPC compared to the past generation’s Goldmont architecture. Sadly, Intel is still mum on the device’s clock speeds. This means that the higher IPC can give more room for lower frequencies as a 10nm process byproduct. If so, it will be similar to the case of Ice Lake processors.

This strategy allowed Intel to mesh two diverse architectures to bank on the efficiency and low-power of the technology’s cores. This, along with Sunny Cove core’s high performance, can create a combination similar to Intel’s hybridx86 architecture.

Behind this architectural fusion is Tremont, the architecture that is always present in other traditional form factors processors.

Single-Sequence Performance

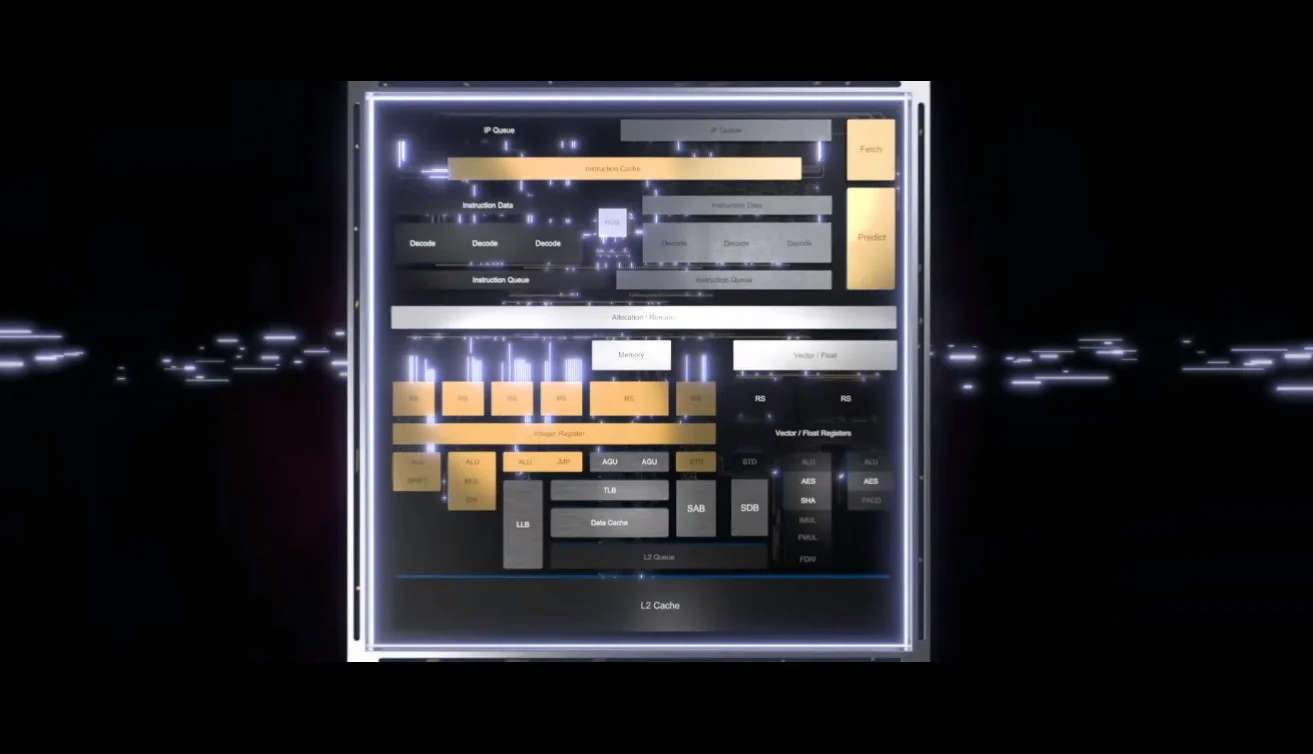

Intel upgraded Tremont’s predictor to a “core-class” performance level. Meaning to say, the Atom cores exhibit the same accuracy level as the high-powered Sunny Cove counterparts. This is achieved by adding a dual-stage prediction implementation. Though Intel hasn’t revealed what type of predictors they used, many suspect they used TAGEin one of its stages.

This architecture can seamlessly decode a maximum of six out-of-order instructions. Aside from that, it also sports a four-wide retire and allocation, equipped with dual store pipelines. This microarchitecture’s chips come in L2 cache-sharing four-core modules that can carry up to 4.5MB.

Final Thoughts

This new microarchitecture from Intel surely looks impressive. In fact, it shows a new performance level in a low-powered space. Then again, Intel still hasn’t shared any specific information on the upcoming SoC’s. Beyond Lakefield, Intel hasn’t shown any clue as to when these next-gen devices will be available to the public.

With this in mind, it is wise not to expect for Tremont cores to be powered by the Goldmont architecture soon. As already observed, an IPC upgrade is not always equal to a massive upgrade in overall performance. The clock speed restrictions in developing process nodes result in a performance slow down.

Then again, the final verdict should be reserved until this technology lands in the market.